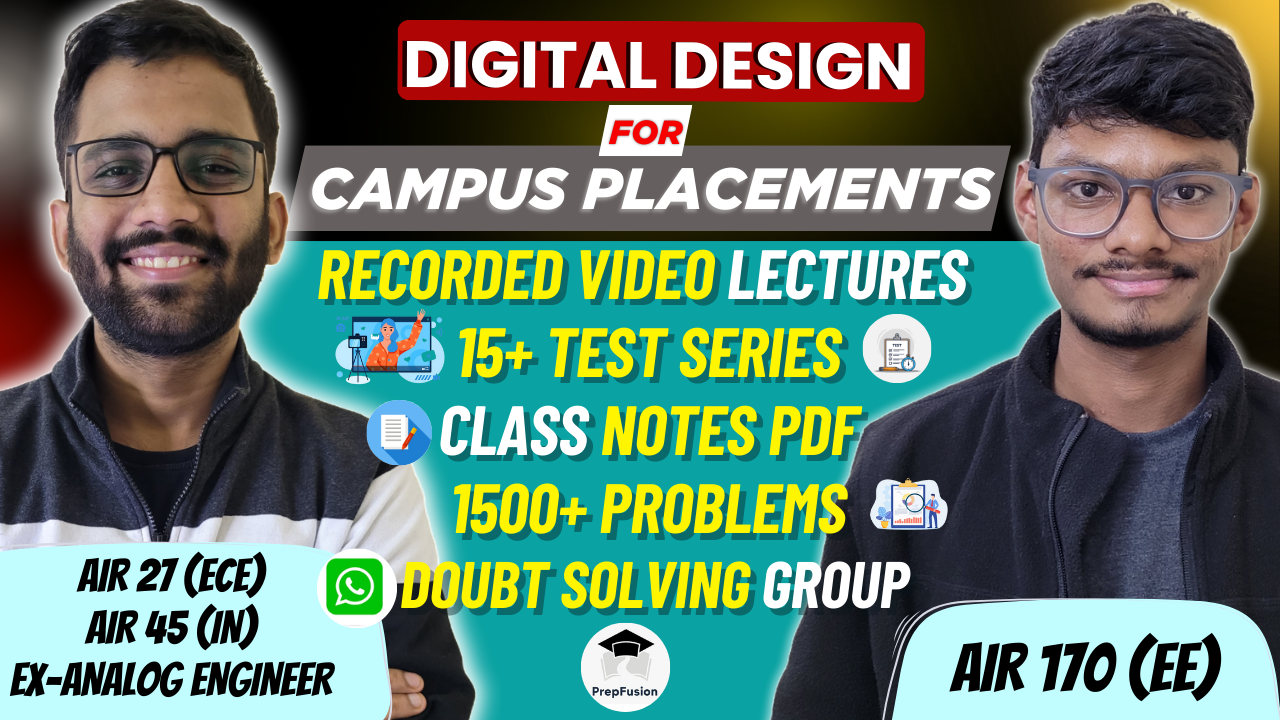

Digital VLSI Mastery - Cohort (0-100) : A Complete Interview + Screening Test Guide {6 Months Validity}

Description

This course covers the whole syllabus of all the subjects required to crack Digital Design Interviews and Screening Test.

With this course, students will be able to prepare themselves for Digital Electronics GATE syllabus, Digital Electronics screening Tests, Digital Design Interviews, M.tech/MS Admission interviews, Interviews for BARC, ISRO, DRDO & All the PSUs.

In this course, you will get

Complete Video Lectures - Fully recorded Video Lectures Covering the complete syllabus for Digital Design Screening Tests, Digital Design interviews, Digital Electronics GATE Syllabus, M.Tech/MS Admission Interviews, Interviews for BARC, ISRO, DRDO & All PSUs. [Both Tech & Aptitude]

Roadmap - Monthly Roadmap to Cover the Whole Course

Lecture Notes - Neatly Written and Downloadable Lecture Notes of each topic. It's recommended to get the Hardcopy of the Lecture Notes before the start of the lecture.

Live Sessions - Doubt Support on WhatsApp Group by Himanshu Agarwal and Anish Saha. Live Sessions will be conducted at least once fortnightly where we discuss doubts, provide guidance regarding Interview, guidance regarding project and resume building.

Test Series : 15+ Topic wise and Subject wise test series will be provided comprising excellent screening test oriented questions specially designed by Himanshu Agarwal and Anish Saha.

Mode of Communication : English

Course Validity : 8 Months

Digital Electronics (80 Hrs) :

1. Boolean Algebra, Logic Gates & K-maps

2. Combinational Circuit

3. Sequential Circuits

4. Finite State Machines

5. Static Timing Analysis

6. Data Converters

7. CMOS VLSI

8. Basic RC Circuits

Verilog HDL (29 Hrs) :

Module 1 (14 Hours) :

VLSI Design Flow

Levels of Abstraction

Values and Signals In Verilog

Keywords & Tokens in Verilog

Event Control

Data Types

Vectors, Arrays, Memories, Parameters

GATE Level Modeling

Continuous Assignments, Operators & Operands

Module 2 (15 Hours) :

Behavioral Modeling

Procedural Assignments

Loops, Parallel & Generate Blocks

Combinational Block Designs:

MUX, Counter, Decoder and Encoder Design

Comparator, 8-Bit Barrel Shifter

Sequential Block Designs: D-Flip Flop, Frequency Divider

Memory Elements Design : FIFO, RAM(Single & Dual Port)

Finite State Machines(FSM) : Mealy & Moore, Vending Machine & Traffic Control Design

Module-2 Exercise Solutions

COA(Computer Organization & Architecture) : 35 HOURS

Chapter - 1 : CPU Architechtures, Instruction Based On Operands, Instruction Cycle, Addressing Modes

Chapter - 2 : Datapath, Control Unit(CU), Instruction Pipelining

Chapter - 3 : Non - Synchronized Pipelines

Chapter - 4 : Floating Point Representation {Important For GATE ECE}

Chapter - 5 : IO Memory Organization

Chapter - 6 : Cache Memory {Very Important For Placements}